在今年初舉行的 CES 展會,Intel 預告於今年發布代號 Tiger Lake 的第十一代 Core SoC 處理器,當時只表示會使用增強版 10nm+ 製程、內建全新的處理核心架構、Xe 顯示核心架構,以及大幅拓展 AI 支援,但架構細節卻一直未有公開。Intel 在上周舉行的 Architecture Day (架構日),終於揭開 Tiger Lake 神秘面紗。

- Intel Tiger Lake 規格揭秘

- Xe 顯示核心‧10nm SuperFin 製程

- 預計在年底節慶季節推出 OEM 系統的客戶

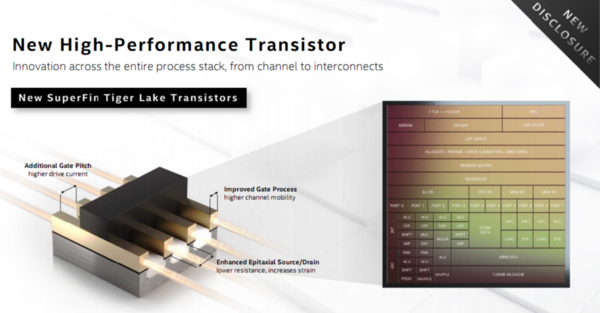

Intel 首席架構師 Raja Koduri 指出,Tiger Lake 使用的新一代 10nm 製程,首次引入革命性 SuperFin 晶體管結構,將增強型 FinFET 晶體、Super MIM (金屬 - 絕緣體 - 金屬) 電容器結合,能夠提供增強的外延源極 / 漏極、改進的柵極工藝、額外的柵極間,效能比初代 10nm 製程 SoC (Ice Lake) 提升超過 15%。此外,Tiger Lake 在相同電壓下,時脈能提高最多 700MHz,而且還可以進一步增加電壓,加速頻率有望達到、甚至突破 5GHz。Tiger Lake 目前正在生產,並出貨予預計在年底節慶季節推出 OEM 系統的客戶。

【精選消息】

【精選消息】

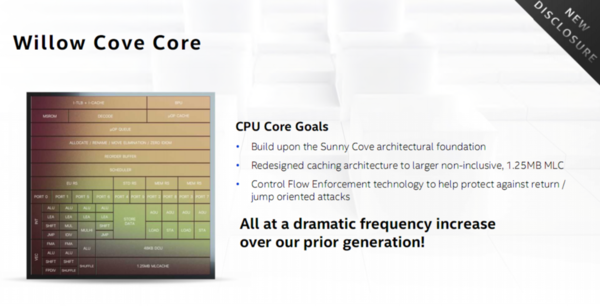

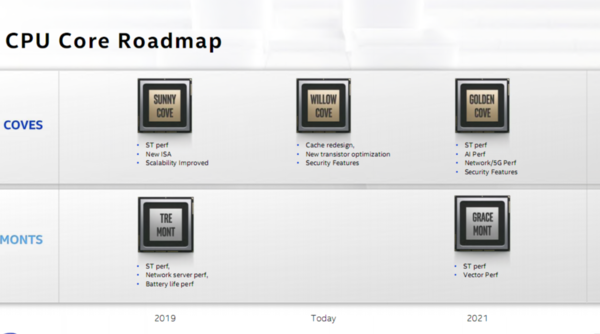

Tiger Lake 的處理核心微架構代號為 Willow Cove,是在目前 Ice Lake 內建的 Sunny Cove 微架構基礎上深度強化,帶來了超過一個世代的 CPU 效能提升幅度,以及大幅度改善時脈表現與提升電力效率。Intel 為 Willow Cove 重新設計快取 (Cache) 架構,每核心的 non-inclusive L2 快取由 512KB 大增至 1.25MB,而 L3 快取也同步升級,並引入 Intel 控制流強制技術 (Control-flow Enforcement Technology) 技術,以加強安全性。

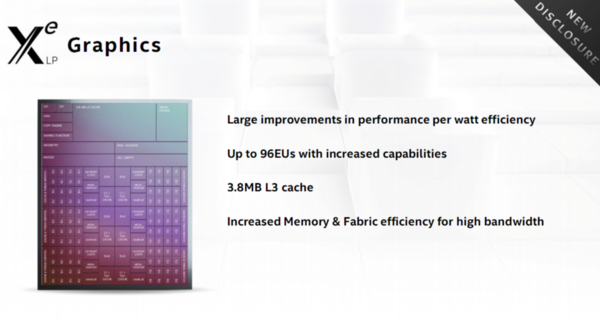

Intel Tiger Lake 首次集成全新設計的 Xe-LP(低功耗)架構顯示核心,大幅改善每瓦效率,最多擁有 96 個 Execution Units (簡稱 E.U.),比 Ice Lake 的最多 64 個 E.U. 增多一半,並配搭獨立 3.8MB L3 快取。此外,Xe-LP 用上最新架構設計,包括:非同步運算、視圖實體化、取樣器回饋、更新支援 AV1 的媒體引擎、更新的顯示引擎等。

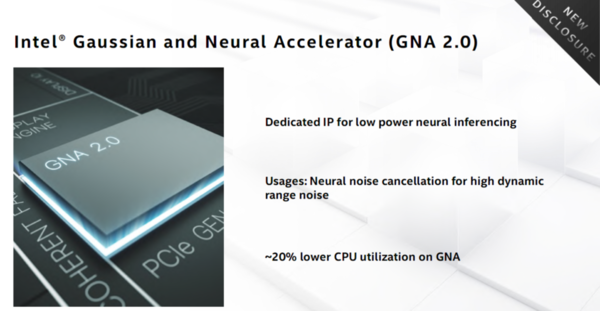

Willow Cove 微架構支援雙通道控制器,對應 DDR4 3,200、LPDDR4X 4,267、LPDDR5 5,400 等,最高頻寬可達 86GB/s,並齊備 Intel 記憶體加密技術 (Total Memory Encryption),直接在硬件層面抵禦安全威脅。AI 方面,Tiger Lake 集成了 GNA (Gaussian and Neural Accelerator) 2.0 加速器,只需低功耗便能以高效進行神經推理運算,並將處理器資源使用率降低 20%,從而提升 AI 效能。

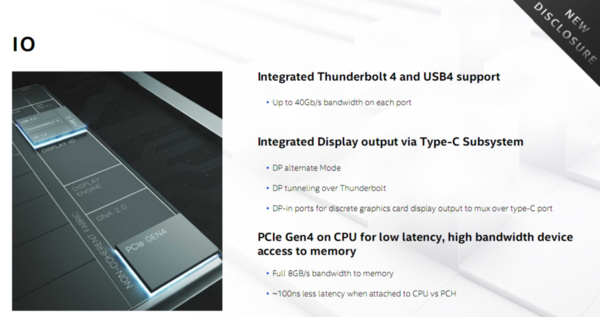

至於 IO 輸入輸出,Tiger Lake 整合新一代 Thunderbolt 4 及 USB 4 控制器,最高頻寬達到 40Gbps。在 Willow Cove 之後,Intel 已準備下一代處理核心微架構,代號為 Golden Cove,並首先應用於明年推出的下一代 Alder Lake 混合式架構處理器。Golden Cove 重點在於提升 ST 核心、AI 效能,同時提升安全性,支援更先進的網絡及 5G 等。

【相關消息】

【相關消息】

Source:Intel