Intel 最新公布代號為 Alder Lake 的第 12 代 Core 處理器架構細節,使用 Intel 7 (前稱 10nm Enhanced Superfin) 製程、大小核心混合 (Hybrid) 架構、引入 Thread Director,並首次在家用平臺支援 DDR5 記憶體及 PCIe 5.0 總綫!

- Intel 公布 12 代 Core Alder Lake 細節

- 大小核混合‧DDR5‧PCIe 5.0 支援

- P-Cores‧E-Cores 混合

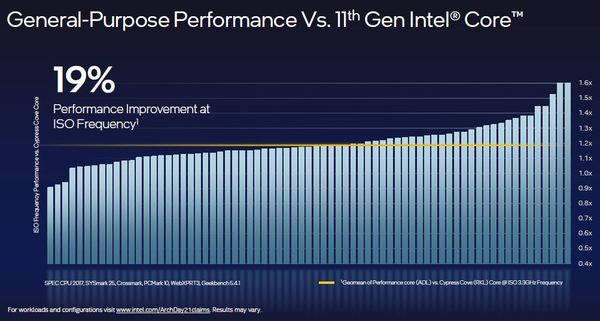

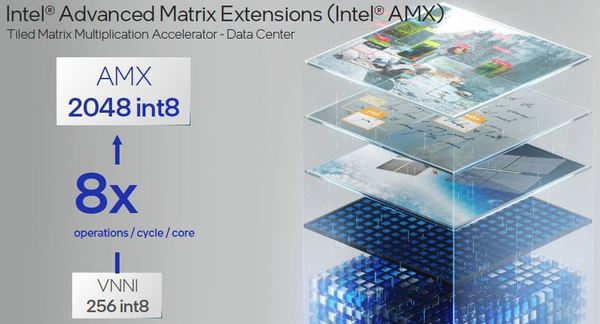

Alder Lake 被 Intel 稱為 x86 架構的一次重大突破,首次採用單晶片集成大小核心混合 (Hybrid) 架構,大核心名為 Performance Cores (P-Cores),屬於 Golden Cove 架構,以高效能為開發目標,最多擁有 8 核心 16 綫程,對應 AVX-512 指令集,提升執行平行度、降低延遲,在同時脈下的 IPC 效能,較 Intel 第 11 代 Core 架構 Cypress Cove 核心提升 19%,此外,更引入全新的 Advanced Matrix Extensions(AMX)機器學習技術。

【精選消息】Intel 發布 Arc 高效顯示品牌!2022 年第一季現身!

【精選消息】Intel 宣布新製程路線圖 20A 製程技術進入埃米時代

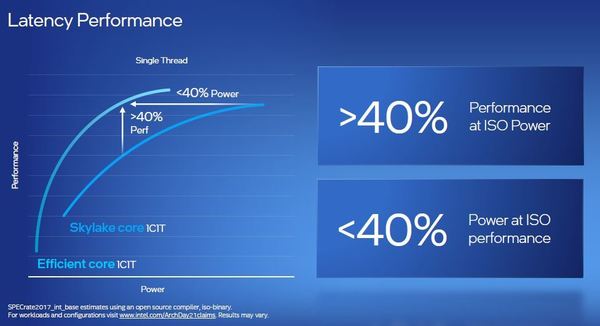

Alder Lake 的小核心名為 Efficiency Cores (E-Cores),屬於 Gracemont 架構,最多 8 核心 8 綫程,以低功耗作賣點,相較於成熟的 Skylake 微架構,E-Cores 單核心在同樣功耗下提供高出 40% 效能,或是在相同效能下,降低 40% 功耗。在多核心處理,4 個 E-Cores 比 4 綫程的 Skylake 雙核心,提供多 80% 效能並降低功耗,或減少 80% 功耗仍維持相同效能。

引入 Thread Director 排程器

Alder Lake 使用 P-Cores 加 E-Cores 混合架構,Intel 為了確保兩者工作無縫接軌,開發出 Thread Director 工作負載排程器,負責監察每個執行緒的性質及效能需求,衡量其載入、存儲、分支、記憶體存取延遲、指令類型等,然後向作業系統調度器 (Scheduler) 報告,由後者結合運行環境,將此執行緒分配到最合適的核心。Intel 指出,Thread Director 可以在最短 30 µs 確定一個執行緒的性質及歸屬,而傳統的系統調度器需要上百甚至幾百 µs,而且有機會分配錯誤。此外,Thread Director 針對應用場景優化時脈,可在流動平台保證指定低耗電下提高效能。Intel 表示已與 Microsoft 緊密合作,保證在《Windows 11》內全面優化 Thread Director 支援。

Alder Lake 可擴展架構

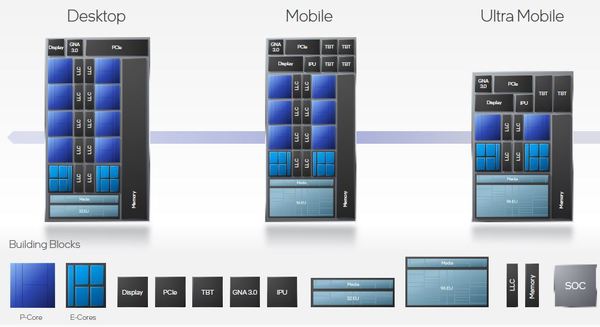

Alder Lake 屬於可擴展架構,覆蓋桌面 (Desktop)、流動 (Mobile) 及超流動 (Ultra Mobile) 平台。

桌面版使用 LGA1700 封裝,最多 8 大 8 小即 16 核心 24 綫程,最高 30MB Cache,TDP 功耗 125W;流動版使用 BGA Type3 整合封裝,大小為 50 x 25 x 1.3mm,最多 6 大 8 小即 14 核心 20 綫程,功耗 12W 至 35W;超流動版則使用 BGA Type4 整合封裝,大小只有 28.5 x 19 x 1.1mm,最多 2 大 8 小即 10 核心 12 綫程,功耗可低至 9W。

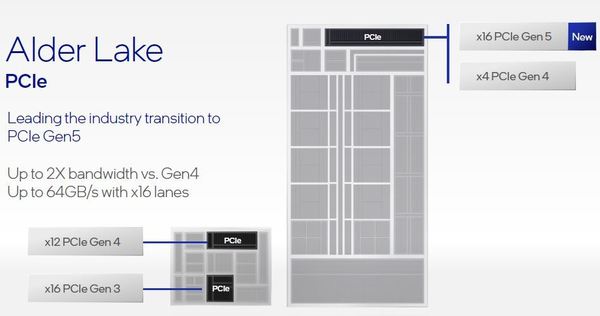

記憶體方面,Alder Lake 桌面版同時支援 DDR5-4800、DDR4-3200、LPDDR5-5200 及 LPDDR4X-4266,而且引入 Dynamic Voltage-Frequency Scaling 技術及強化超頻。PCIe 連接方面,桌面版支援 16 條 PCIe 5.0 總綫提供高達 64GB/s 頻寬,另設 4 條 PCIe 4.0 供連接高速 NVMe SSD。

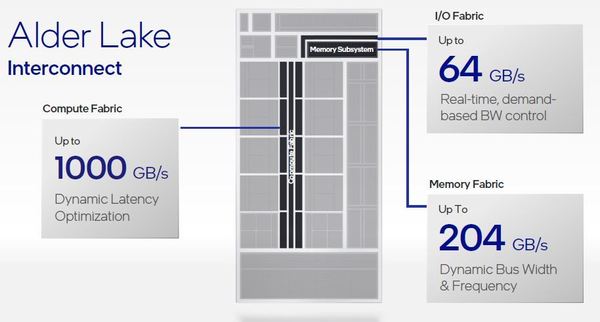

內部互連方面,Alder Lake 提供三種高速通道,包括:Compute Fabric:主要連接 CPU 核心、快取記憶體,頻寬可達 1,000GB/s,並支援動態緩存優化;Memory Fabric,連接記憶體和其他模組,頻寬最高 204GB/s,支援動態位元寬和頻率;I/O Fabric 用戶輸入輸出,最高頻寬 64GB/s,支援基於需求的即時頻寬控制。

【相關報道】Intel 旗下自駕車成首輛在紐約街頭試行車輛 靠 12 個鏡頭自主於繁忙街道穿梭

【相關報道】Intel CEO 預測晶片短缺問題持續 今年下半年將觸底反彈

即刻【按此】,用 App 睇更多產品開箱科技影片

Source: Intel