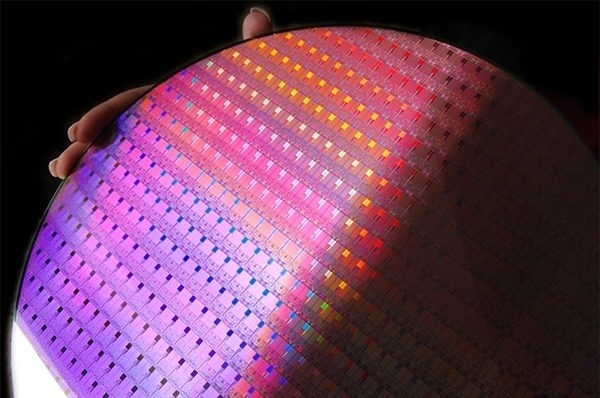

隨著半導體工藝深入到5nm以下,製造的難度和成本日益增加。摩爾定律的物理極限大約在1nm左右,再往下就會面臨嚴重的量子隧穿難題,這將導致晶體管失效。當然,各大廠商在實際尺寸上採用的先進工藝都有一定的餘地,因此紙面上的1nm工藝仍然可能存在。去年,台積電組建了一個團隊來研發1.4nm工藝,最近CEO劉德音表示公司正在探索比1.4nm更先進的工藝。

隨著半導體工藝深入到5nm以下,製造的難度和成本日益增加。摩爾定律的物理極限大約在1nm左右,再往下就會面臨嚴重的量子隧穿難題,這將導致晶體管失效。當然,各大廠商在實際尺寸上採用的先進工藝都有一定的餘地,因此紙面上的1nm工藝仍然可能存在。去年,台積電組建了一個團隊來研發1.4nm工藝,最近CEO劉德音表示公司正在探索比1.4nm更先進的工藝。

↓↓↓同場加映:【e+同你試】ASUS Zenfone 10 全新旗艦手機 設計小巧單手拍攝無難度↓↓↓

即刻【按此】,用 App 睇更多產品開箱影片

快科技報道,台積電去年成立了一個團隊來研發1.4nm工藝。最近,台積電的CEO劉德音表示公司正在探索比1.4nm更先進的工藝。 1.4nm工藝是半導體行業追求的目標之一,因為再往下就是1nm工藝,但這也會面臨很大的挑戰。根據去年IMEC歐洲微電子中心公佈的路線圖顯示,2nm工藝之後是14A,也就是1.4nm工藝,預計2026年問世,再往後就是A10工藝,也就是1nm,預計在2028年問世。當然,實際能夠量產的時間可能會比2028年晚一些,因為新技術的開發通常難免會遇到一些延誤。

在2nm節點之後的新工藝研發和生產中,EUV光刻機也需要進行一次大規模升級。根據ASML的計劃,他們預計在2026年推出下一代EUV光刻機EXE:5000系列,該系列採用High NA技術,將NA指標從當前的0.33提升到0.55,可以進一步提高光刻分辨率。但是,下一代EUV光刻機的代價也非常高。售價將從目前的1.5億美元上升到4億美元以上,最終價格可能還會上漲。 30億美元的設備價格非常考驗製造商的成本控制能力。

【熱門報道】

【熱門報道】

Source:快科技