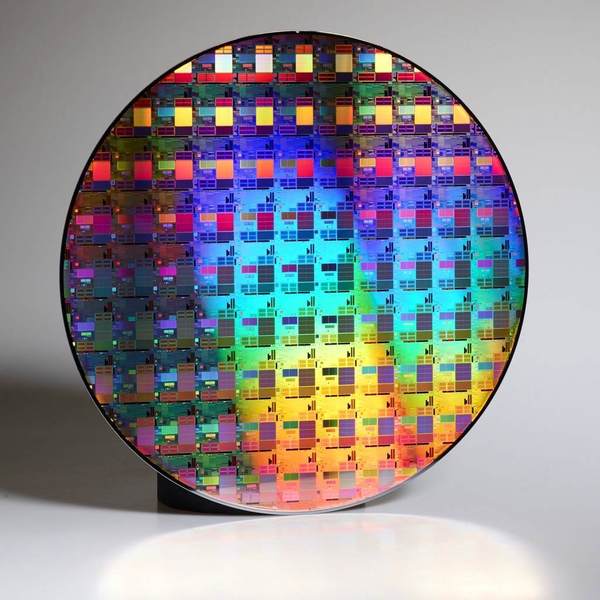

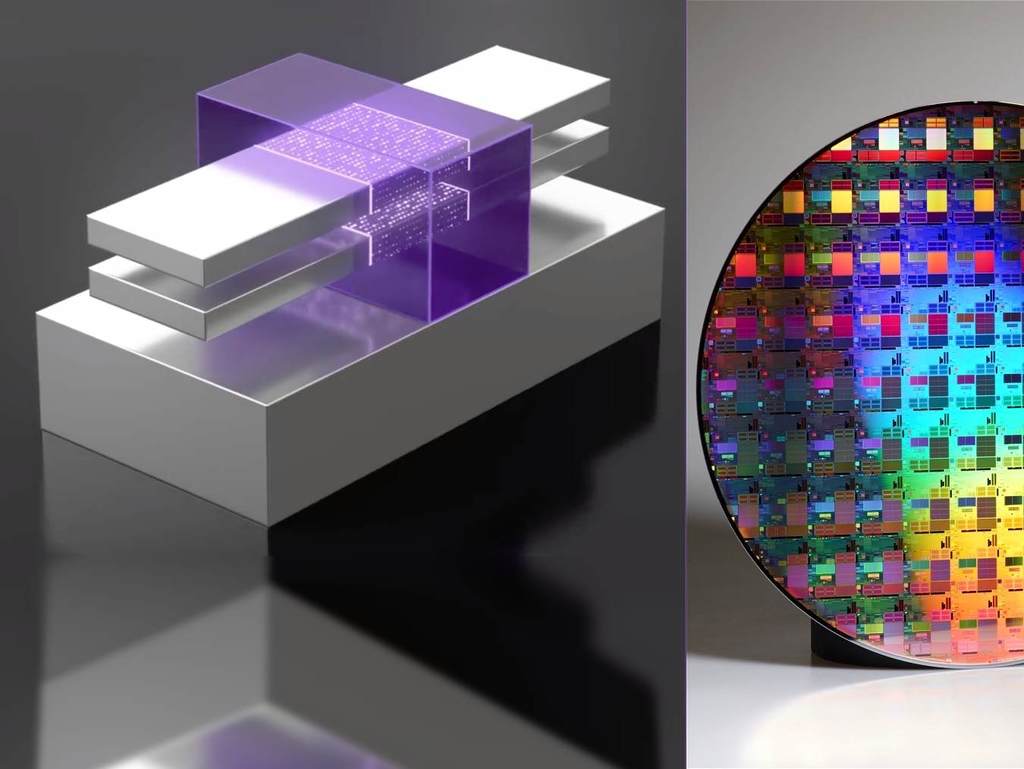

Samsung 宣佈計劃 2030 年前投產 3nm 製程的矽晶圓盤 (Silicon Wafer),屆時市場上的 DRAM 記憶體、NAND Flash 快閃記憶體,以至 Samsung 自家 Exynos 系列手機處理器,將達到超低功耗時代。技術重點是 Samsung 自家 GAAFET (Gate All Around FET) 晶片技術,取代現時 FinFET (Fin field-effect FET),在更小空間下,1 條通道 (Channel) 能讓更多閘極 (Gate) 通過。

- 2030 年前量產 3nm 晶片

- 改良電晶體及電路結構

- 投資額高達 1,118.5 億美元

【硬件】AMD「Navi 21」GPU 效能勁升 RDNA2 架構全曝光

【硬件】Intel LGA1200 十代 Core 型號全公開!傳明年 2 月上市

製程單位數值愈細,代表晶片內部電晶體佈線,結構可以造得愈複雜。現時 Samsung (三星) 與 TSMC (台積電) 均有能力生產 7nm EUVL 製程的晶片,雙方也計劃發展 5nm,然而 Samsung 已明確計劃生產 3nm 晶片,目標是 2030 年前。晶片內部佈線,其實仿如建築物的間格,垂直的「牆」稱為 Gate (閘極);穿過 Gate 的「鋼筋」線路,則稱為 Channel (通道)。

現時 7nm 及 FinFET 技術下,Gate 造得較高,左側、頂端、右側共 3 個表面,能與 Gate 接觸。但未來 3nm 及 GAAFET 技術下,Channel 將大幅縮小,讓可多達 3 條直接貫穿 Gate。由於每條 Channel 的橫切面積是呈長方形,有 4 個表面;3 條 Gate 便等於 12 個表面,能與 Gate 接觸,大幅提高晶片內部線路的使用效率,而且能承受 30GHz 級數超高時脈。

Samsung 表示將投資 1,118.5 億美元,在南韓建設 3nm GAAFET 矽晶圓盤生產廠房。雖然要 2030 至 2031 年,才開始有 3nm 晶片產品,但其實與用家息息相關。屆時 DRAM、NAND Flash、手機處理器、電腦平台 GPU 等,若以 3nm GAAFET 製程,晶片體積將極細小,電晶體 (Transistors) 數量大幅提高,令容量或效能均能大幅加強,但功耗卻極低。

【硬件】Intel 1.4nm 製程 2029 年面世!未來十年光刻技術版圖

【硬件】AMD Ryzen 4000 APU 將有六核心? 7nm 製程‧二代 Vega 內顯

Source:ezone.hk、Wccftech